## RF MEMS Capacitive Switches Fabricated with HDICP CVD SiN<sub>x</sub>

C.H. Chang, J.Y. Qian, B.A. Cetiner, Q. Xu, M. Bachman, H.K. Kim\*, Y. Ra\*, F. De Flaviis and G.P. Li

Electrical and Computer Engineering Department, University of California at Irvine, Irvine, CA 92697

\*Bethel Material Research, Placentia, CA 92870, USA

**Abstract** — The role of very low temperature (90-170°C) high density inductively coupled plasma chemical vapor deposition (HDICP CVD) process in RF MEMS switch fabrication is addressed. The results on SiN<sub>x</sub> layers produced by both HDICP CVD and plasma enhanced CVD (PECVD) are compared in terms of surface roughness, breakdown voltage and RF MEMS switch performance. It is found that HDICP CVD can provide very thin (250 Å) nitride layer having root mean square (rms) roughness value of 1.6 nm at very low temperature (90°C). The breakdown strength is measured to be 9MV/cm. A SiN<sub>x</sub> layer with these characteristics improves the device reliability and dramatically increases its down position capacitance providing additional degree of freedom in RF MEMS switch design.

### I. INTRODUCTION

RF MEMS switches have been becoming increasingly attractive in many communications applications in which very low loss is the critical issue. Although RF MEMS switches do not have as higher speed as that of their semiconductor counterparts (pin diode, FET), they have very low insertion loss due to the low resistivity of metal, high isolation due to the physical separation of the switch, and excellent linearity with the elimination of I-V nonlinearities, which are inevitable for pin diode or FET associated with semiconductor junctions. This low loss feature of the MEMS switches makes them very attractive for use in modern radar and communications system where thousands of switches are employed. The cost of individual RF MEMS switch is still higher than pin diode or FET. On the other hand, the advantage of MEMS switches of allowing monolithic batch fabrication when they are used as system components in an integrated RF system makes the overall system cost cheaper than the system in which pin diode, for example, is used as a switching component that requires hybrid assembly.

The conceptual simplicity of MEMS technology (implementation is not necessarily simple), its promising future and the use of standard IC equipments and fabrication techniques for their implementation encourages many industry and university research groups to work on this area. While initial MEMS work was performed in

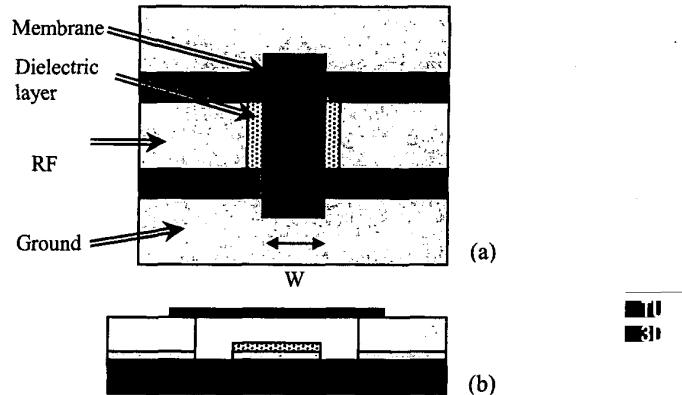

Fig. 1 Schematic of RF MEMS capacitive switch (a) Top view, (b) Side view

1960's and first products appeared in the market in 1970's the RF MEMS is a new emerging sub area of MEMS technology. Due to its new nature there are many fabrication issues that have to be addressed and solved in order to improve fabrication yield and build state of the art, reliable RF MEMS devices.

In this paper, we first present coplanar waveguide (CPW) RF MEMS switches fabricated on glass substrate using conventional fabrication processes. The measured and simulated results showing the performance of the device are also provided. In section III, as an effort to improve the performance and reliability of the device, we report a novel fabrication process, HDICP CVD, for use in place of PECVD process. The HDICP CVD nitride film quality was characterized and compared to those of films deposited using PECVD. It was observed that HDICP CVD SiN<sub>x</sub> layer has better surface roughness and higher breakdown voltage than conventional SiN<sub>x</sub> layer. In addition, the better pinhole characteristics of HDICP CVD process allow us to deposit very thin layer of nitride (250 Å), which improves the RF MEMS switch isolation performance. The I-V curve showing the breakdown voltage of the nitride layer of 250 Å is given. Finally, two sets of RF MEMS switches having the same dimensions

were fabricated using HDICP CVD and PECVD processes and tested. The comparative results showed the improvement in device performance when HDICP CVD is used for  $\text{SiN}_x$  deposition.

## II. RF MEMS SWITCH DESCRIPTION, FABRICATION AND CHARACTERIZATION

The topology of the RF MEMS switches (See Figs.1a and 1b) here presented is similar to the one described in the paper of Yao, et al [1]. It consists of a CPW transmission line with a metallic membrane suspended on top of a signal electrode of the CPW line. The details on the design, fabrication and modeling for the similar RF MEMS switches can be found in [2].

In our device Cu is used as a metal since it is widely used in the semiconductor industry owing to its performance, low cost and low resistivity characteristics. In addition Cu allows selective deposition eliminating many etching processes otherwise necessary, and allows fewer process steps. For the membrane, however, we used Al alloy since Cu does not have a good fatigue property that limits the lifetime of the device. As a substrate glass material is used, although the process is compatible with other substrates such as GaAs and Si. One of the reasons choosing glass is its lower cost. The other one is its recent popularity in microwave applications. Although glass is not a very good microwave substrate in terms of its electrical characteristics ( $\epsilon_r=5.8-7$ , loss tangent=0.003-0.005), its use is usually dictated by the microwave application itself such as a smart microwave antenna system integrated with RF MEMS switches embedded in the rear or front screen of the car used as part of a sophisticated electronic control system.

The RF MEMS switches were fabricated by utilizing surface micromachining techniques. The 4-mask fabrication includes the process steps of electron-beam metal deposition, Cu electroplating, PECVD and HDICP CVD dielectric deposition, sacrificial layer planarization, reactive-ion etching (RIE) and selective wet etching. The brief process description is as follows: A  $0.2\text{ }\mu\text{m}$  electron-beam Ti/Cu seed layer is first deposited and patterned to define ground and signal line of the CPW. A thin layer of PECVD  $\text{SiN}_x$  is deposited and patterned by using RIE such that it only covers the central part of the signal line. To define the region for the electroplating Cu, a photoresist layer is spun on and patterned. The ground plane and signal line except its central part that is covered by a dielectric layer defining signal electrode are Cu electroplated to a thickness of  $4\mu\text{m}$ . A  $0.5\text{ }\mu\text{m}$  electron-beam Al alloy layer is deposited and wet etched to define the membranes. As a last step of the fabrication processes

the membranes are released by removing the sacrificial photoresist layer using acetone, ethanol and a critical-point drying system.

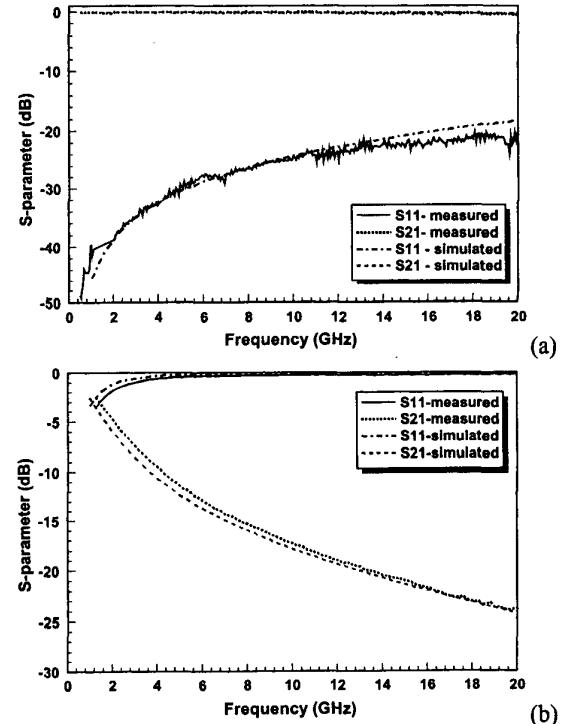

RF measurements were performed using a HP 8510C network analyzer connected to the Cascade probe station. The measurements were calibrated using thru-reflection-line (TRL) on-wafer standards. The two-port s-parameters of the device were recorded for 1-20 GHz. Ideally, a switch would have a zero insertion loss in the on (up position) state such that its input port is connected without any loss to its output port, and infinite attenuation in the off (down position) state, in other words ideal disconnection between its input and output ports. In reality, of course, they show some insertion loss for the on state and finite attenuation for the off state. Fig. 2 illustrates the measured and simulated S-parameters of the fabricated switch with the membrane width of  $W=150\mu\text{m}$ . It shows a good switching performance for both on and off state. The agreement between simulation and measurement proves the accuracy of the simulation tool used. Indeed, accurate simulation tools can be used to obtain scalable switch model having desired S-parameters for the intended applications [3].

Fig. 2 Measured and calculated S-parameters for the RF MEMS switch in (a) the on state and (b) off state

Table I: Comparison of *RMS* roughness (nm) between HDICP CVD and PECVD.

| HDICP CVD  |             |             | PECVD |          |

|------------|-------------|-------------|-------|----------|

| 500W, 90°C | 500W, 170°C | 800W, 170°C | 250°C | 300°C[1] |

| 1.6        | 2.0         | 2.2         | 2.5   | 3.1      |

### III. HDICP CVD PROCESS AND CHARACTERIZATION

The fabrication processes with low temperature feature offer some important improvements in RF MEMS technology. For example, in nowadays RF MEMS integrated antenna systems, substrates are usually dictated by the process limitations, especially the high temperature processes. However, these substrates usually with high dielectric constant and high loss tangent values are not the most appropriate ones to achieve desired impedance behavior and radiation characteristics of the antenna elements required by the advanced communication systems. On the other hand, low temperature processes allow us to fabricate antennas, as well as, RF MEMS parts of the integrated system on any substrate possessing required electrical characteristics for the antenna elements.

In our fabrication process we are using a novel equipment for low temperature chemical vapor deposition (CVD). Based on this device's patent-pending plasma technology, which utilizes inductively coupled plasma principle, very high-density plasmas at very low temperature (90-170 °C) allows the deposition of various thin films. By the use of HDICP CVD, in order to improve RF MEMS switch performance and reliability, we aimed at to deposit higher quality SiN<sub>x</sub> layers with smooth surface, higher breakdown voltage, and less pin hole density.

To improve the switching performance by achieving a desired high capacitance ratio, which is given by,

$$\frac{C_{down}}{C_{up}} = \frac{\epsilon_r t_{air} + t_{diel}}{t_{diel}} \quad (1)$$

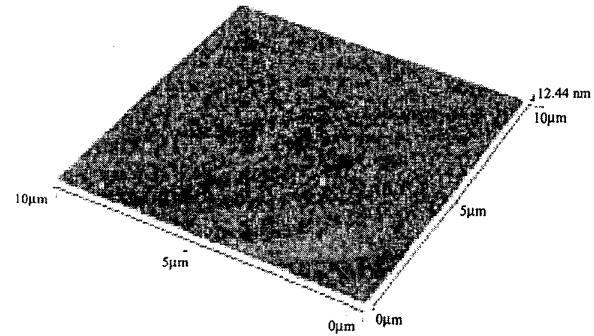

the down state capacitance ( $C_{down}$ ) must be as high as possible. In equation (1),  $t_{air}$  and  $t_{diel}$  are the thicknesses of the air and dielectric layers beneath the membrane. Surface roughness of the SiN<sub>x</sub> film is one of the parameters that plays a critical role at the down position capacitance. The smooth surface of the nitride film provides intimate contact with the metal membrane so that contact area is increased providing higher capacitance. Fig. 3 shows the atomic force microscopy (AFM) measurement of the surface of 0.1μm SiN<sub>x</sub> film deposited by HDICP CVD on top of a Ti/Cu seed layer at the condition of 90°C and

500W. The root-mean-square (*RMS*) roughness is 1.6nm. RMS is defined as,

$$RMS = \sqrt{\frac{1}{N} \sum_{i=1}^N (Z_i - \bar{Z})^2} \quad (2)$$

where,  $N$  is the number of data points,  $Z_i$  the height value, and  $\bar{Z}$  the image height mean value. Table I compares RMS roughness of HDICP CVD and PECVD SiN<sub>x</sub> films with a thickness of 0.1μm. The results indicate that the SiN<sub>x</sub> films deposited at lower temperatures possess smaller *RMS* roughness. It should be noted herein that the low temperature feature of this HDICP CVD prevents metal electrode, on which SiN<sub>x</sub> is deposited, from being exposed to high temperatures that may cause hillock problems [1].

Fig. 3: AFM micrograph of the 500W, 90°C SiN<sub>x</sub> surface.

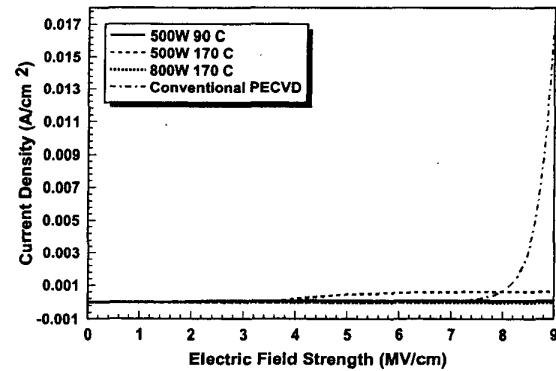

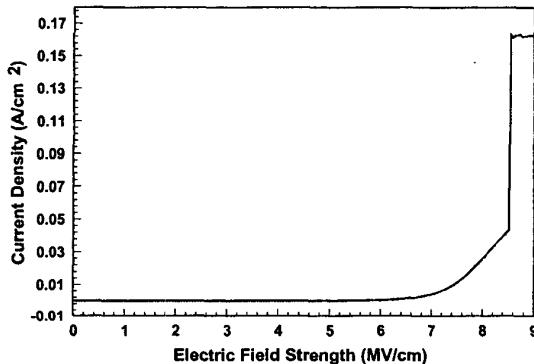

Fig. 4: I-V characteristics of HDICP CVD and PECVD SiN<sub>x</sub> films.

Fig. 4 shows the I-V behavior of  $0.1\mu\text{m}$   $\text{SiN}_x$  films deposited by HDICP CVD and PECVD. The observed breakdown strengths of the three HDICP CVD  $\text{SiN}_x$  films are larger than 9 MV/cm, which is higher than the typical corresponding operating voltage of RF MEMS switches. The PECVD  $\text{SiN}_x$  film shows a soft breakdown behavior, that is, no abrupt current jump. It should be pointed out that the film has much higher leakage current at the high electric field compared to the HDICP CVD films.

The other parameter to increase the capacitance ratio given by Equation (1) is the thickness of the  $\text{SiN}_x$  layer. The thinner the  $\text{SiN}_x$  film is, the higher the capacitance ratio. As indicated in the paper of Muldavin, et al [2], it is impractical to deposit, by using PECVD,  $\text{SiN}_x$  films thinner than  $0.1\mu\text{m}$  since large pinhole density that results in low dielectric breakdown strength. Fig. 5 shows the I-V curves of the 800W-170 °C  $\text{SiN}_x$  film of 250 Å. The breakdown voltage is 9 MV/cm. Based on the results in Figs.4 and 5, the HDICP CVD  $\text{SiN}_x$  films with the thickness of as thin as 250 Å can be used in RF MEMS switch devices withstanding the typical actuation voltage (20-50V) without dielectric breakdown.

Fig. 5: I-V curves of the HDICP CVD  $\text{SiN}_x$  film of 250 Å.

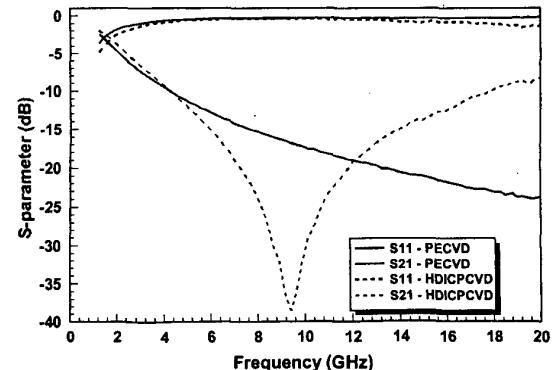

Finally, we fabricated two sets of switch by using PECVD and HDICP CVD processes to compare their performances. As seen from fig.6 the isolation of the HDICP CVD switch is better than the one fabricated using PECVD for the frequency range of from 4 to 12GHz. It shows a resonant at 9 GHz proving the dramatic increase in down position capacitance. It is worth noting, however, the fabrication has many process steps and the switches compared are not exactly identical so that there are more parameters playing a role on their overall performances.

Fig. 6 Comparison of switches fabricated by HDICP CVD and PECVD processes.

## V. CONCLUSION

This paper presented a novel very low temperature (90-170°C) HDICP CVD process and its use in RF MEMS switch fabrication. Characterization of the HDICP CVD  $\text{SiN}_x$  films showed significant improvements in film quality in terms of surface roughness, breakdown voltage and pin hole density. A  $\text{SiN}_x$  layer of the thickness as thin as 250 Å with breakdown voltage of 9 MV/cm having very smooth surface (RMS=1.6nm) can be deposited using this technique. In addition, the low temperature feature of this process allows choosing substrate materials possessing desired electrical characteristics for the RF MEMS integrated communication systems. This novel process technique must play an important role in fabrication of the state-of-the-art, reliable RF MEMS devices.

## REFERENCES

- [1] Z.J. Yao, S. Chen, S. Eshelman, D. Denniston and C. Goldsmith, "Micromachined low-loss microwave switches," *IEEE Journal of Microelectromechanical Systems*, vol. 8, no. 2, pp. 129-134, June 1999.

- [2] J. B. Muldavin, G. M. Rebeiz, "High-isolation CPW MEMS shunt switches: Modeling and Design," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-48, no. 6, pp. 1045-1056, June 2000.

- [3] J. Y. Qian, G. P. Li, F. De Flaviis, "A Parametric Model Of Mems Capacitive Switch Operating At Microwave Frequencies", *2000 IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, pp. 1229-32, June 2000.